The Max 10 Datasheet is a critical document for anyone working with Intel's versatile MAX 10 Field Programmable Gate Arrays (FPGAs). It serves as the definitive source of information, detailing the specifications, capabilities, and operational parameters of these powerful devices. Understanding the Max 10 Datasheet is fundamental to successfully designing, implementing, and optimizing your embedded systems. This document is your key to unlocking the full potential of the MAX 10 FPGA family.

What is the Max 10 Datasheet and How is it Used?

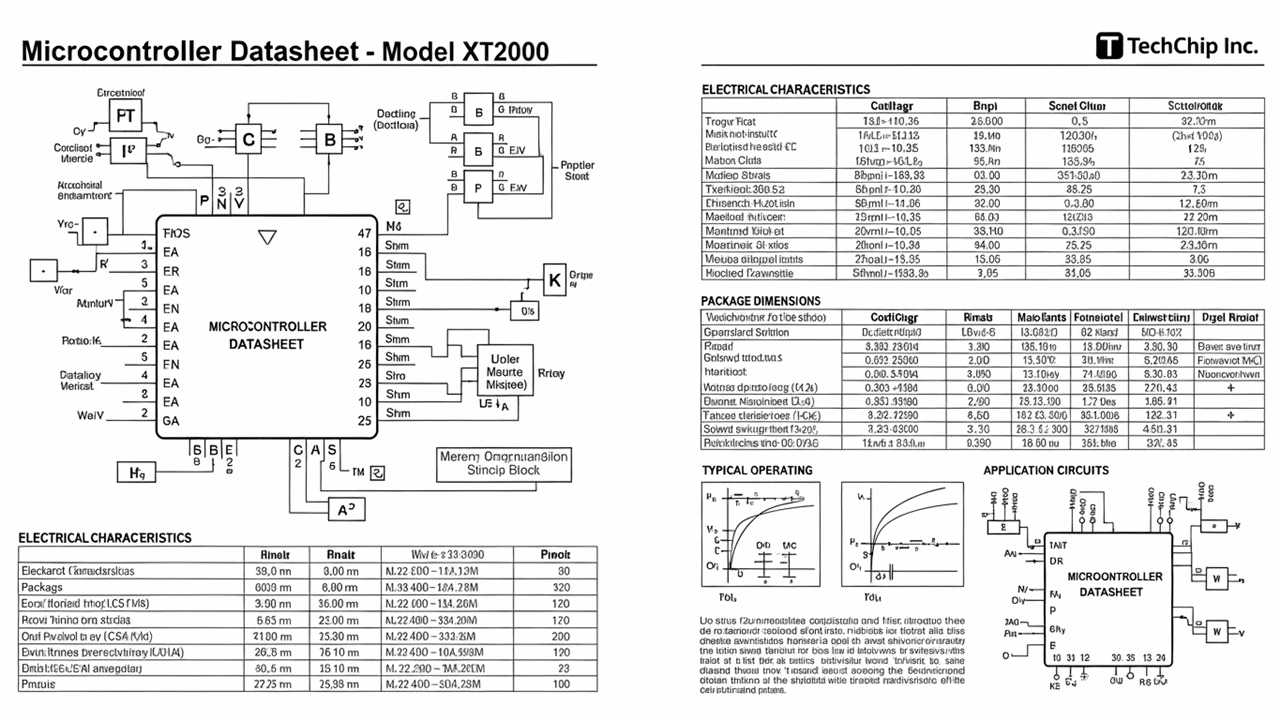

At its core, the Max 10 Datasheet is a comprehensive technical reference manual. It provides an in-depth look at the MAX 10 FPGA's architecture, including details on logic elements, memory blocks, digital signal processing (DSP) blocks, and input/output (I/O) capabilities. Engineers and designers rely on this document to understand the performance characteristics of the chip, such as speed grades, power consumption, and operating conditions. The importance of thoroughly reviewing the Max 10 Datasheet cannot be overstated, as it directly impacts design choices and system reliability.

The datasheet is used in various stages of the design process. During the initial selection phase, it helps engineers choose the right MAX 10 device for their specific application by comparing different variants and their features. For example, the table below highlights some key differentiating factors:

| Feature | MAX 10 Base | MAX 10 with ADC |

|---|---|---|

| On-chip ADC | No | Yes |

| Flash Memory | Integrated | Integrated |

| Logic Elements | Varies by device | Varies by device |

Furthermore, the Max 10 Datasheet is indispensable for detailed design and verification. It provides crucial information for configuring I/O pins, understanding timing constraints, and ensuring the device operates within its specified limits. Designers will find detailed sections on:

- Electrical characteristics

- Pin assignments and package information

- Power-on reset and configuration details

- Thermal considerations

It also outlines various operational modes and the procedures for programming and configuring the FPGA, often involving a sequence of steps like:

- Power-up the device.

- Load the configuration bitstream into the SRAM.

- Initialize internal logic.

This methodical approach ensures that the FPGA is correctly set up and ready to execute the designed logic.

To fully grasp the intricacies and leverage the full capabilities of the MAX 10 FPGAs, we strongly recommend consulting the official Max 10 Datasheet. It's the definitive resource for all technical details.